# Al Chips: What They Are and Why They Matter

An Al Chips Reference

**AUTHORS**

Saif M. Khan Alexander Mann

# Table of Contents

| Introduction and Summary                                                        | 3  |

|---------------------------------------------------------------------------------|----|

| The Laws of Chip Innovation                                                     | 7  |

| Transistor Shrinkage: Moore's Law                                               | 7  |

| Efficiency and Speed Improvements                                               | 8  |

| Increasing Transistor Density Unlocks Improved Designs for Efficiency and Speed | 9  |

| Transistor Design is Reaching Fundamental Size Limits                           | 10 |

| The Slowing of Moore's Law and the Decline of General-Purpose Chips             | 10 |

| The Economies of Scale of General-Purpose Chips                                 | 10 |

| Costs are Increasing Faster than the Semiconductor Market                       | 11 |

| The Semiconductor Industry's Growth Rate is Unlikely to Increase                | 14 |

| Chip Improvements as Moore's Law Slows                                          | 15 |

| Transistor Improvements Continue, but are Slowing                               | 16 |

| Improved Transistor Density Enables Specialization                              | 18 |

| The Al Chip Zoo                                                                 | 19 |

| Al Chip Types                                                                   | 20 |

| Al Chip Benchmarks                                                              | 22 |

| The Value of State-of-the-Art AI Chips                                          | 23 |

| The Efficiency of State-of-the-Art AI Chips Translates into Cost-Effectiveness  | 23 |

| Compute-Intensive AI Algorithms are Bottlenecked by Chip Costs and Speed        | 26 |

| U.S. and Chinese Al Chips and Implications for National Competitiveness         | 27 |

| Appendix A: Basics of Semiconductors and Chips                                  | 31 |

| Appendix B: How AI Chips Work                                                   | 33 |

| Parallel Computing                                                              | 33 |

| Low-Precision Computing                                                         | 34 |

| Memory Optimization                                                             | 35 |

| Domain-Specific Languages                                                       | 36 |

| Appendix C: Al Chip Benchmarking Studies                                        | 37 |

| Appendix D: Chip Economics Model                                                | 39 |

| Chip Transistor Density, Design Costs, and Energy Costs                         | 40 |

| Foundry, Assembly, Test and Packaging Costs                                     | 41 |

| Acknowledgments                                                                 | 44 |

|                                                                                 |    |

# Introduction and Summary

Artificial intelligence will play an important role in national and international security in the years to come. As a result, the U.S. government is considering how to control the diffusion of Al-related information and technologies. Because general-purpose AI software, datasets, and algorithms are not effective targets for controls, the attention naturally falls on the computer hardware necessary to implement modern AI systems. The success of modern Al techniques relies on computation on a scale unimaginable even a few years ago. Training a leading AI algorithm can require a month of computing time and cost \$100 million. This enormous computational power is delivered by computer chips that not only pack the maximum number of transistors basic computational devices that can be switched between on (1) and off (0) states—but also are tailor-made to efficiently perform specific calculations required by AI systems. Such leading-edge, specialized "AI chips" are essential for cost-effectively implementing AI at scale; trying to deliver the same Al application using older Al chips or general-purpose chips can cost tens to thousands of times more. The fact that the complex supply chains needed to produce leading-edge AI chips are concentrated in the United States and a small number of allied democracies provides an opportunity for export control policies.

This report presents the above story in detail. It explains how AI chips work, why they have proliferated, and why they matter. It also shows why leadingedge chips are more cost-effective than older generations, and why chips specialized for AI are more cost-effective than general-purpose chips. As part of this story, the report surveys semiconductor industry and AI chip design

trends shaping the evolution of chips in general and AI chips in particular. It also presents a consolidated discussion of technical and economic trends that result in the critical cost-effectiveness tradeoffs for AI applications.

In this paper, AI refers to cutting-edge computationally-intensive AI systems, such as deep neural networks. DNNs are responsible for most recent AI breakthroughs, like DeepMind's AlphaGo, which beat the world champion Go player. As suggested above, we use "AI chips" to refer to certain types of computer chips that attain high efficiency and speed for AI-specific calculations at the expense of low efficiency and speed for other calculations.\*

This paper focuses on AI chips and why they are essential for the development and deployment of AI at scale. It does not focus on details of the supply chain for such AI chips or the best targets within the supply chain for export controls (CSET has published preliminary results on this topic<sup>1</sup>). Forthcoming CSET reports will analyze the semiconductor supply chain, national competitiveness, the prospects of China's semiconductor industry for supply chain localization, and policies the United States and its allies can pursue to maintain their advantages in the production of AI chips, recommending how this advantage can be utilized to ensure beneficial development and adoption of AI technologies.

This report is organized as follows:

Industry Trends Favor AI Chips over General-Purpose Chips

From the 1960s until the 2010s, engineering innovations that shrink transistors doubled the number of transistors on a single computer chip roughly every two years, a phenomenon known as Moore's Law. Computer chips became millions of times faster and more efficient during this period. (Section II.)

<sup>\*</sup> Our definition of "AI chips" includes graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and certain types of application-specific integrated circuits (ASICs) specialized for AI calculations. Our definition also includes a GPU, FPGA, or AI-specific ASIC implemented as a core on system-on-a-chip (SoC). AI algorithms can run on other types of chips, including general-purpose chips like central processing units (CPUs), but we focus on GPUs, FPGAs, and AI-specific ASICs because of their necessity for training and running cutting-edge AI algorithms efficiently and quickly, as described later in the paper.

The transistors used in today's state-of-the-art chips are only a few atoms wide. But creating even smaller transistors makes engineering problems increasingly difficult or even impossible to solve, causing the semiconductor industry's capital expenditures and talent costs to grow at an unsustainable rate. As a result, Moore's Law is slowing—that is, the time it takes to double transistor density is growing longer. The costs of continuing Moore's Law are justified only because it enables continuing chip improvements, such as transistor efficiency, transistor speed, and the ability to include more specialized circuits in the same chip. (Section III and IV.)

The economies of scale historically favoring general-purpose chips like central processing units have been upset by rising demand for specialized applications like AI and the slowing of Moore's Law-driven CPU improvements. Accordingly, specialized AI chips are taking market share from CPUs. (Section V.)

#### Al Chip Basics

Al chips include graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs) that are specialized for AI. General-purpose chips like central processing units (CPUs) can also be used for some simpler AI tasks, but CPUs are becoming less and less useful as AI advances. (Section V(A).)

Like general-purpose CPUs, Al chips gain speed and efficiency (that is, they are able to complete more computations per unit of energy consumed) by incorporating huge numbers of smaller and smaller transistors, which run faster and consume less energy than larger transistors. But unlike CPUs, Al chips also have other, Al-optimized design features. These features dramatically accelerate the identical, predictable, independent calculations required by AI algorithms. They include executing a large number of calculations in parallel rather than sequentially, as in CPUs; calculating numbers with low precision in a way that successfully implements Al algorithms but reduces the number of transistors needed for the same calculation; speeding up memory access by, for example, storing an entire Al algorithm in a single AI chip; and using programming languages built specifically to efficiently translate AI computer code for execution on an AI chip. (Section V and Appendix B.)

Different types of AI chips are useful for different tasks. GPUs are most often used for initially developing and refining AI algorithms; this process is known as "training." FPGAs are mostly used to apply trained AI algorithms to realworld data inputs; this is often called "inference." ASICs can be designed for either training or inference. (Section V(A).)

# Why Cutting-Edge AI Chips are Necessary for AI

Because of their unique features, AI chips are tens or even thousands of times faster and more efficient than CPUs for training and inference of Al algorithms. State-of-the-art AI chips are also dramatically more cost-effective than state-of-the-art CPUs as a result of their greater efficiency for AI algorithms. An AI chip a thousand times as efficient as a CPU provides an improvement equivalent to 26 years of Moore's Law-driven CPU improvements. (Sections V(B) and VI(A) and Appendix C.)

Cutting-edge AI systems require not only AI-specific chips, but state-of-the-art Al chips. Older Al chips—with their larger, slower, and more power-hungry transistors—incur huge energy consumption costs that quickly balloon to unaffordable levels. Because of this, using older AI chips today means overall costs and slowdowns at least an order of magnitude greater than for state-ofthe-art AI chips. (Section IV(B) and VI(A) and Appendix D.)

These cost and speed dynamics make it virtually impossible to develop and deploy cutting-edge AI algorithms without state-of-the-art AI chips. Even with state-of-the-art AI chips, training an AI algorithm can cost tens of millions of U.S. dollars and take weeks to complete. In fact, at top AI labs, a large portion of total spending is on Al-related computing. With general-purpose chips like CPUs or even older AI chips, this training would take substantially longer to complete and cost orders of magnitude more, making staying at the research and deployment frontier virtually impossible. Similarly, performing inference using less advanced or less specialized chips could involve similar cost overruns and take orders of magnitude longer. (Section VI(B).)

#### Implications for National AI Competitiveness

State-of-the-art AI chips are necessary for the cost-effective, fast development and deployment of advanced security-relevant AI systems. The United States and its allies have a competitive advantage in several semiconductor industry sectors necessary for the production of these chips. U.S. firms dominate Al

chip design, including electronic design automation (EDA) software used to design chips. Chinese AI chip design firms are far behind and are dependent on U.S. EDA software to design their AI chips. U.S., Taiwanese, and South Korean firms control the large majority of chip fabrication factories ("fabs") operating at a sufficiently advanced level to fabricate state-of-the-art AI chips, though a Chinese firm recently gained a small amount of comparable capacity. Chinese AI chip design firms nevertheless outsource manufacturing to non-Chinese fabs, which have greater capacity and exhibit greater manufacturing quality. U.S., Dutch, and Japanese firms together control the market for semiconductor manufacturing equipment (SME) used by fabs. However, these advantages could disappear, especially with China's concerted efforts to build an advanced chip industry. Given the security importance of state-of-the-art AI chips, the United States and its allies must protect their competitive advantage in the production of these chips. Future CSET reports will analyze policies for the United States and its allies to maintain their competitive advantage and explore points of control for these countries to ensure that the development and adoption of AI technologies increases global stability and is broadly beneficial for all. (Section VII.)

# The Laws of Chip Innovation

All computer chips—including general-purpose CPUs and specialized ones like AI chips—benefit from smaller transistors, which run faster and consume less energy than larger transistors. Compared to CPUs, AI chips also gain efficiency and speed for Al applications through Al-optimized designs. However, at least while transistor shrinkage came at a fast rate and produced large speed and efficiency gains through the late 2000s, the value of specialized designs remained low and CPUs were the dominant chip. However, Moore's Law is close to driving transistors to fundamental size limits at atomic scales. For a basic introduction to chips, see Appendix A.

Transistor Shrinkage: Moore's Law

Moore's Law states that the number of transistors in a chip doubles about every two years. Technical innovations that shrink transistors allow increased transistor density. Moore's Law was first observed in the 1960s, and it held until the 2010s, when improvements in transistor density began slowing. Today, leading chips contain billions of transistors, but they have 15 times fewer transistors than they would have if Moore's Law had continued.<sup>2</sup>

Transistor density increases occur in generations, or "nodes." Each node corresponds to the transistor size (expressed in terms of length) that allows a doubling of transistor density relative to the previous node. Fabs began "risk production," i.e. experimental production, of the latest node of 5 nanometers ("nm") in 2019, with mass production expected in 2020.3 The previous leading nodes were 7 nm and 10 nm.4

A companion principle to Moore's Law says that because smaller transistors generally use less power than larger ones, as transistor density increases, power consumption per unit chip area remains constant.<sup>5</sup> However, transistor power reduction rates slowed around 2007.6

### Efficiency and Speed Improvements

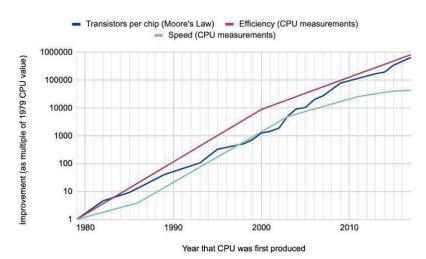

CPU speed has improved prodigiously since the 1960s due in large part to Moore's Law. Greater transistor density improved speed primarily via "frequency scaling," i.e. transistors switching between ones and zeros faster to allow more calculations per second by a given execution unit. Because smaller transistors use less power than larger ones, transistor switching speeds could be increased without increasing total power consumption. Figure 1 shows transistor density, speed, and efficiency improvements since 1979.

Between 1978 and 1986, frequency scaling drove 22 percent annual increases in speed. Then, between 1986 and 2003, speed increased by 52 percent annually, due to frequency scaling and design improvements enabling simultaneous calculations to be performed through parallel computing. As frequency scaling slowed, parallelism enabled by multi-core designs powered 23 percent annual speedups between 2003 and 2011. Exploitation of the final remnants of available CPU parallelism brought 12 percent annual gains between 2011 and 2015, after which progress on CPU speed slowed to three percent per year.8

Efficiency has also improved dramatically. Because decreased transistor size reduces power use per transistor, overall CPU efficiency during peak chip usage doubled every 1.57 years until 2000.9 Since then, due to the slowing of transistor power reduction, efficiency has doubled every 2.6 years, equivalent to a 30 percent per year efficiency improvement.<sup>10</sup>

Figure 1: CPU improvement rates normalized relative to 1979<sup>11</sup>

Increasing Transistor Density Unlocks Improved Designs for Efficiency and Speed

As transistors shrink and density increases, new chip designs become possible, further improving efficiency and speed. First, CPUs can include more and different types of execution units optimized for different functions. 12 Second, more on-chip memory can reduce the need for accessing slower offchip memory. Memory chips such as DRAM chips likewise can pack more memory. 13 Third, CPUs can have more space for architectures that implement parallel rather than serial computation. Relatedly, if increased transistor density enables smaller CPUs, then a single device can house multiple CPUs (also called multiple "cores"), which each run different computations at once.

In the 1990s, design improvement lagged behind transistor density improvement because chip design firms struggled to exploit design possibilities unlocked by rapidly increasing transistor availability. 14 To get around this bottleneck, design firms focused comparatively more on trailing nodes (chips several generations behind the leading-edge), outsourced the brute-force work of creating a large number of chip designs to lower-paid engineers abroad, reused portions ("IP cores") of previous designs, and used EDA software to translate high-level abstract designs—easier for design engineers to work with—into concrete transistor-level designs. 15

#### Transistor Design is Reaching Fundamental Size Limits

As transistors have shrunk to sizes only a few atoms thick, they are fast approaching fundamental lower limits on size. Various physics problems at small scales also make further shrinkage more technically challenging. The first significant change arrived in the 2000s when the transistor's insulative layer became so thin that electrical current started leaking across it. 16 Engineers used new, more insulative materials and stopped shrinking the insulative layer even as other components continued to shrink.<sup>17</sup>

More dramatic structural changes followed. From the 1960s to 2011, key transistors were manufactured as thin layers stacked on top of each other.<sup>18</sup> Yet even the more insulative materials could not prevent leakage. Instead, engineers replaced this planar arrangement with a more complex threedimensional structure. This new structure has been dominant from the 22 nm node—released in 2011—to the current 5 nm node. 19 However, beyond 5 nm, even this structure leaks. A completely new structure has been developed for the future 3 nm node;<sup>20</sup> it includes components measuring only a few atoms in thickness, making further shrinkage beyond 3 nm challenging.<sup>21</sup>

# The Slowing of Moore's Law and the Decline of General-Purpose Chips

Today, the trends that sustained CPU progress and primacy over specialized chips are ending. Technical difficulties are increasing the costs of Moore's Law improvements at a faster rate than the growth of the semiconductor market. Ultimately, these economic and technical factors suggest actual transistor densities will fall further behind what Moore's Law predicts and that we may reach the point of no further significant improvements in transistor densities.<sup>22</sup>

#### The Economies of Scale of General-Purpose Chips

The steady improvement in transistor-switching speeds and transistor power reduction favored CPUs over specialized chips. In the era of general-purpose chip dominance, specialized chips could not generate enough sales volume to recoup steep design costs.<sup>23</sup> Specialized chips earn their task-specific improvements over CPUs from design. But when rapid frequency scaling was still producing large speed and efficiency benefits, the computing premium from specialized chips was quickly erased by next-generation CPUs, whose

costs were spread across millions of chip sales.<sup>24</sup> Today, the slowing of Moore's Law means that CPUs no longer quickly improve. This results in longer useful lifetimes of specialized chips, making them more economical.

Costs are Increasing Faster than the Semiconductor Market

Increasing technical difficulties at small scales have driven up the costs of high-end semiconductor research and development across the supply chain. Different sectors of the semiconductor industry have localized in different regions based on their comparative advantages.<sup>25</sup>

The highest-value sectors, particularly SME, fabs, and chip design, have seen especially steep rates of cost growth and consolidation.<sup>26</sup> Annual growth rates in the cost of semiconductor fabrication facilities (eleven percent) and design costs per chip (24 percent) are faster than those of the semiconductor market (seven percent).<sup>27</sup> And the approximate number of semiconductor R&D workers has been increasing seven percent per year.

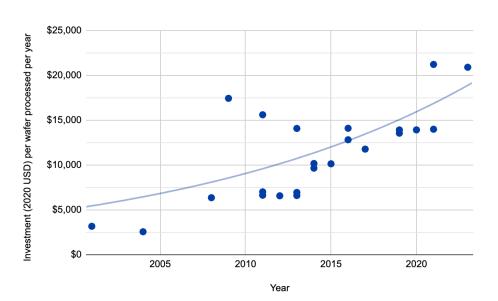

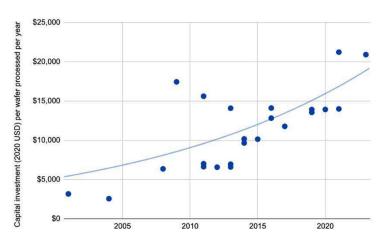

Since the early 2000s, the growth rate of semiconductor fabrication costs, including costs of fabs and SME, has trended at 11 percent per year. Fixed costs increasing faster than variable costs has created higher barriers of entry, squeezing fab profits and shrinking the number of chipmakers operating fabs at the leading nodes.<sup>28</sup> Figure 2 shows increasing construction costs of the largest fabs owned by Taiwan Semiconductor Manufacturing Company (TSMC). Currently, there are only two chipmakers at the 5 nm node: TSMC in Taiwan and Samsung in South Korea. Intel follows at 10 nm with plans to introduce the 7 and 5 nm nodes: GlobalFoundries and Semiconductor Manufacturing International Corporation (SMIC) lag at 14 nm (see Table 1).29

Figure 2: TSMC's leading-edge fab costs<sup>30</sup>

Costs of photolithography tools, the most expensive and complex segment of SME, have risen from \$450,000 per unit in 1979 to \$123 million in 2019.³¹ And only one photolithography company, ASML in the Netherlands, now sells photolithography equipment capable of manufacturing the smallest 5 nm transistors. Nikon in Japan is the only other company making a significant volume of photolithography tools that operate at ≤90 nm (see Table 1). Eventually, increasing research and development costs for photolithography equipment and fabs at the leading node may prevent even a natural monopoly from recouping costs from the slowly growing global semiconductor market.

Table 1: Number of companies at each node

| Node (nm)                                | 180  | 130  | 90   | 65   | 45/<br>40 | 32/<br>28 | 22/20 | 16/<br>14 | 10   | 7    | 5    |

|------------------------------------------|------|------|------|------|-----------|-----------|-------|-----------|------|------|------|

| Year mass production                     | 1999 | 2001 | 2004 | 2006 | 2009      | 2011      | 2014  | 2015      | 2017 | 2018 | 2020 |

| Chipmakers <sup>32</sup>                 | 94   | 72   | 48   | 36   | 26        | 20        | 16    | 11        | 5    | 3    | 3    |

| Photolithography companies <sup>33</sup> | 4    | 3    | 2    | 2    | 2         | 2         | 2     | 2         | 2    | 2    | 1    |

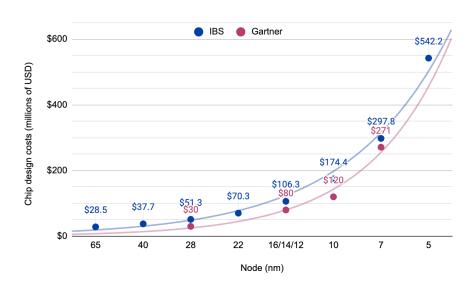

Meanwhile, as shown in Figure 3, multiple estimates suggest the cost of chip design has been rising exponentially. When matched with TSMC's node introduction dates, design costs per node according to International Business Strategies (IBS) yields a 24 percent yearly cost increase.<sup>34</sup> Due to their general-purpose usage, CPUs enjoy economies of scale enabling U.S. firms Intel and AMD to maintain a decades-long duopoly in CPU design for servers and personal computers (PCs), such as desktops and laptops.<sup>35</sup>

Figure 3: Chip design costs at each node<sup>36</sup>

As semiconductor complexity increases, demands for high-end talent drive design and fabrication cost overruns. The effective number of researchers, measured by dividing semiconductor R&D spending by wages of high-skilled workers, saw an 18x increase from 1971 to 2015.<sup>37</sup> Put another way, a Moore's Law doubling required eighteen times as much human research effort in 2015 than in 1971, representing a seven percent increase per vear.38

Overall design and manufacturing cost per transistor may be the best metric to measure whether transistor density improvements remain economical. This cost has historically decreased by around 20-30 percent annually.<sup>39</sup> Some analysts claim that decreases have stopped past the 28 nm node introduced in 2011, while others disagree.<sup>40</sup>

# The Semiconductor Industry's Growth Rate is Unlikely to Increase

Unless new chip applications cause growth rates to increase, the semiconductor industry is unlikely to see growth rates sufficient to accommodate the industry's increasing costs. The semiconductor market is already growing at a faster rate than the world economy's three percent rate. Currently, the semiconductor industry produces 0.5 percent of global economic output. Due in part to the trade war between the United States and China, the semiconductor market shrunk in 2019.<sup>41</sup> However, it typically exhibits a year-to-year sawtooth growth trajectory, so a multi-year slowing would better indicate a slowing in long-run growth.<sup>42</sup>

# Chip Production at Each Node

Given the technical and economic challenges of chip production, new nodes are being introduced more slowly than in the past. Intel, the standard bearer of Moore's Law, has indeed slowed node introduction. It introduced 32 and 22 nm nodes two years after their predecessors, consistent with Moore's Law, but 14 nm followed three years after 22 nm, and 10 nm four years after 14 nm node chips. 43 Yet the leading foundry services vendor, TSMC, has not slowed node introduction.44

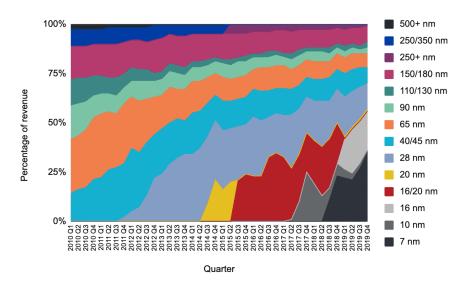

Trends in leading node chip sales volumes do not yet suggest a major slowing in the adoption of new nodes. From 2002 to 2016, TSMC's leading node stably represented approximately 20 percent of its revenue.<sup>45</sup> TSMC's 10 nm and 7 nm nodes introduced in 2016 and 2018, respectively, also reached 25 percent and 35 percent respectively, as shown in Figure 4.

TSMC's stable sales rates of new nodes—though slower than in the early 2000s—may mask the fact that the foundry services market as a whole is slowing adoption. TSMC has controlled roughly half of the world's foundry services market share for the last decade. 46 Rising production costs are reducing the number of companies at the leading node. For example, during this time, GlobalFoundries dropped out by failing to progress beyond 14 nm. If this trend is accompanied by less fab capacity at the current leading node than was the case for previously leading nodes, it would indicate that Moore's Law is slowing.47

Fabs still make chips at the old nodes shown in Figure 4 for several reasons. Fabs incur great costs to build leading fabs or upgrade old ones to manufacture chips at newer nodes, so immediately transitioning world fab capacity to leading nodes is not possible. Instead, fabs continue selling old nodes at lower prices, especially to customers for whom purchase cost is the primary criterion. Many of these customers may be less concerned about efficiency because their applications are not computationally intensive. Similarly, their applications may not require fast speeds or otherwise may complete computations fast enough on old chips. Additionally, some specialized low-volume products like analog chips require trailing nodes to remain cost-effective.49

# Chip Improvements as Moore's Law Slows

As Moore's Law slows, chips continue to improve in two ways: efficiency and speed improvements of smaller transistors, and efficiency and speed improvements from advanced chip designs exploiting larger numbers of transistors per chip enabled by smaller transistor size. These advanced designs include the ability to pack more specialized cores on a single chip.<sup>50</sup>

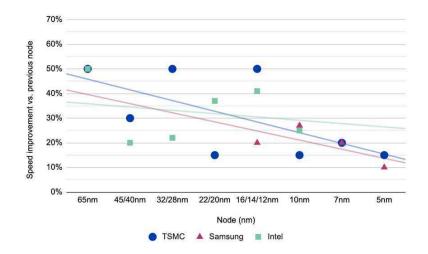

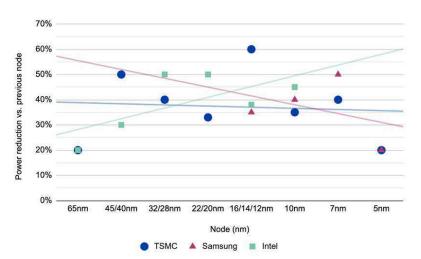

Fortunately, some speed and efficiency improvements are still available, but with considerable technical challenges. Around 2004, when the 65 nm node was reached, transistor density improvements slowed in reducing transistor power usage and increasing transistor switching speed (frequency scaling).<sup>51</sup> Nevertheless, fabs report that transistor-level rather than design-level innovation continues to provide consistent, albeit slowing, improvements from node to node. TSMC and Samsung claim their 5 nm node chips improve upon the transistor speed of their 7 nm node chips respectively by 15 and 10 percent with power usage held constant<sup>52</sup> and reduce power usage by 30 and 20 percent with transistor speed held constant.<sup>53</sup> Figures 5 and 6 show a downward trend in TSMC's claimed node-to-node transistor speed improvements at constant efficiency between 90 nm and 5 nm, but a flat trend in TSMC's claimed transistor power reduction improvements.<sup>54</sup> Samsung trends downward between 14 nm and 5 nm on both metrics, but we lack data at nodes larger than 14 nm. 55 Intel sees slightly dropping transistor speed improvements, <sup>56</sup> but continuing node-to-node transistor power reduction improvements from 65 nm to 10 nm. <sup>57</sup> Intel has not yet introduced its 7 nm node. These improvements in speed and efficiency benefit both general-purpose chips like CPUs and specialized chips like AI chips.<sup>58</sup>

Figure 5: Node-to-node transistor speed improvements

Figure 6: Node-to-node transistor power reduction improvements

Chip design improvements now provide decreasing CPU efficiency and speed improvements. Figure 7 consolidates the speed and efficiency measurements by node, both for CPUs and for transistors. For CPUs, we use data from Figure 1. For transistors, we use data for TSMC's and Intel's nodes from Figures 5 and 6.59 The sources roughly agree on speed and efficiency improvements. TSMC's and Intel's reported improvements, derived from transistor-level innovation, generally match CPU improvements derived from both transistor-level and design-level innovation. The rough match implies that transistor-level innovation<sup>60</sup> has continued to play a major role in CPU efficiency and speed improvements over the last 15 years, <sup>61</sup> at least for the measured CPU benchmarks.<sup>62</sup> Efficient designs, however, do still play a role.63

50.0 Multiplicative improvement vs. 90 nm node 40.0 30.0 20.0 10.0 0.0 45/40nm 32/28nm 22/20nm 16/14/12nm Node Transistor efficiency (TSMC) Transistor efficiency (Intel) CPU efficiency Transistor speed (TSMC) Transistor speed (Intel) CPU speed

Figure 7: Measured efficiency and speed improvements against 90 nm

#### Improved Transistor Density Enables Specialization

Besides improving transistor function, increasing transistor density enables chips to include more varieties of specialized circuits that perform different types of calculations.<sup>64</sup> A chip can call upon a different specialized circuit depending on which calculation is requested. These circuits can include some optimized for AI algorithms and others specialized for different types of calculations. Al chips, which will be discussed in section V, are chips entirely specialized for AI.

Outside of the use of these specialized circuits, in recent years there has been little left to gain by adding more transistors to general-purpose chips. More transistors could theoretically enable a CPU to include more circuits to perform a larger number of calculations in parallel. However, speedups from parallelism are commonly limited by the percentage of time spent on serial computations, computations performed one after the other because the result of one computation is needed to start another. Parallel computations, conversely, are performed simultaneously. Even when only one percent of an algorithm's calculation time requires serial calculations, 45 percent of processor energy is wasted.<sup>65</sup> Unfortunately, most applications require at least some serial computation, and processor energy waste becomes too high as the serialization percentage increases. As other design improvements have slowed since the mid-2000s, multi-core designs with ever larger numbers of cores have proliferated. But multi-core designs also cannot efficiently

parallelize algorithms requiring a significant percentage of time spent on serial computations.

# The AI Chip Zoo

The trend toward chips specialized for AI applications is driven by two factors. First, as discussed in Section IV, the critical improvements in semiconductor capabilities have shifted from manufacturing to design and software. 66 Second, an increasing demand for applications like AI requires highly parallelizable, predictable computations that benefit from specialized chips.<sup>67</sup> Deep neural networks (DNNs)—AI algorithms responsible for most recent AI breakthroughs—fit this bill. DNNs usually implement a type of machine learning called supervised learning, which involves two computing steps: "training" an Al algorithm based on training data (i.e. building the algorithm) and executing the trained AI algorithm (i.e. performing "inference") to classify new data consistent with knowledge acquired from data in the training stage. The training step in particular often requires performing the same computation millions of times. As discussed in Section IV(B), improved transistor density allows more types of specialized circuits on a single chip. Al chips take this to the extreme—the layout of most or all transistors on the chip is optimized for the highly parallelizable, specialized computations required by AI algorithms.

Although analysts disagree widely on the size of the global AI chip market— 2018 estimates ranged between \$5 and \$20 billion—they agree that the market will grow faster than for chips not specialized for AI.<sup>68</sup> Until recently, a small number of firms designing general-purpose chips like CPUs dominated the logic chip design market. They enjoyed economies of scale that enabled them to reinvest into powerful new CPU designs. However, the slowing of Moore's Law is damaging CPU producers' economies of scale; now specialized chips have longer useful lifetime before Moore's Law-driven CPU efficiency and speed gains overcome the benefits of specialized chips. Therefore, the ability of CPU design firms to reinvest in new designs to maintain market dominance is declining. This trend lowers barriers to entry for chip design startups—especially those focused on specialized chips.<sup>69</sup>

Al chips are a common type of specialized chip, and share some features in common. Al chips execute a much larger number of calculations in parallel than CPUs. They also calculate numbers with low precision in a way that successfully implements AI algorithms but reduces the number of transistors

needed for the same calculation. They also speed up memory access by storing an entire AI algorithm in a single AI chip. Finally, AI chips use programming languages specialized to efficiently translate AI computer code to execute on an AI chip. For more detail on these techniques, see Appendix B.

While general-purpose chips include a small number of popular designs, particularly the CPU, AI chips are more diverse. AI chips vary widely in design, the applications they are suited to, efficiency and speed for different AI tasks, generality, and classification accuracy when performing inference. The following subsections categorize AI chips along these axes.

# Al Chip Types

Al chips include three classes: graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs).<sup>70</sup>

GPUs were originally designed for image-processing applications that benefited from parallel computation. In 2012, GPUs started seeing increased use for training AI systems and by 2017, were dominant.<sup>71</sup> GPUs are also sometimes used for inference.<sup>72</sup> Yet in spite of allowing a greater degree of parallelism than CPUs, GPUs are still designed for general-purpose computing.<sup>73</sup>

Recently, specialized FPGAs and ASICs have become more prominent for inference, due to improved efficiency compared to GPUs.<sup>74</sup> ASICs are increasingly used for training, as well.<sup>75</sup> FPGAs include logic blocks (i.e. modules that each contain a set of transistors) whose interconnections can be reconfigured by a programmer after fabrication to suit specific algorithms, while ASICs include hardwired circuitry customized to specific algorithms. Leading ASICs typically provide greater efficiency than FPGAs, while FPGAs are more customizable than ASICs and facilitate design optimization as Al algorithms evolve.<sup>76</sup> ASICs, by contrast, grow increasingly obsolete as new Al algorithms are developed.

Different AI chips may be used for training versus inference, given the various demands on chips imposed by each task. First, different forms of data and model parallelism are suitable for training versus inference, as training requires additional computational steps on top of the steps it shares with

inference. Second, while training virtually always benefits from data parallelism, inference often does not. For example, inference may be performed on a single piece of data at a time. However, for some applications, inference may be performed on many pieces of data in parallel, especially when an application requires fast inference of a large number of different pieces of data. Third, depending on the application, the relative importance of efficiency and speed for training and inference can differ. For training, efficiency and speed are both important for AI researchers to cost-effectively and quickly iterate research projects. For inference, high inference speed can be essential, as many AI applications deployed in critical systems (e.g. autonomous vehicles) or with impatient users (e.g. mobile apps classifying images) require fast, real-time data classification. On the other hand, there may be a ceiling in useful inference speed. For example, inference need not be any faster than user reaction time to a mobile app. 77

Inference chips require fewer research breakthroughs than training chips, as they require optimization for fewer computations than training chips. And ASICs require fewer research breakthroughs than GPUs and FPGAs; because ASICs are narrowly optimized for specific algorithms, design engineers consider far fewer variables. To design a circuit meant for only one calculation, an engineer can simply translate the calculation into a circuit optimized for that calculation. But to design a circuit meant for many types of calculations, the engineer must predict which circuit will perform well on a wide variety of tasks, many of which are unknown in advance.

An AI chip's commercialization has depended on its degrees of general-purpose capability. GPUs have long been widely commercialized, as have FPGAs to a lesser degree. Meanwhile, ASICs are more difficult to commercialize given high design costs and specialization-driven low volume. However, a specialized chip is relatively more economical in an era of slow general-purpose chip improvement rates, as it has a longer useful lifetime before next-generation CPUs attain the same speedup or efficiency. In the current era of slow CPU improvements, if an AI chip exhibits a 10-100x speedup, then a sales volume of only 15,000-83,000 should be sufficient to make the AI chip economical. The projected market size increase for AI chips could create the economies of scale necessary to make ever narrower-capability AI ASICs profitable.

Al chips come in different grades, from more to less powerful. At the highend, server grade Al chips are commonly used in data centers for high-end applications and are, after packaging, larger than other AI chips. At the medium-end are PC grade AI chips commonly used by consumers. At the low-end, mobile AI chips are typically used for inference and integrated into a system-on-a-chip that also includes a CPU. A mobile system-on-a-chip needs to be miniaturized to fit into mobile devices. At each of these grades, Al chip market share increases have come at the expense of non-Al chips.<sup>80</sup>

Supercomputers have limited but increasing relevance for Al. Most commonly, server grade chips are distributed in data centers and can be executed sequentially or in parallel in a setup called "grid computing." A supercomputer takes server grade chips, physically co-locates and links them together, and adds expensive cooling equipment to prevent overheating. This setup improves speed but dramatically reduces efficiency, 81 an acceptable tradeoff for many applications requiring fast analysis. Few current Al applications justify the additional cost of higher speed, but training or inference for large AI algorithms is sometimes so slow that supercomputers are employed as a last resort. 82 Accordingly, although CPUs have traditionally been the supercomputing chip of choice, 83 Al chips are now taking an increasing share.84 In 2018, GPUs were responsible for the majority of added worldwide supercomputer computational capacity.<sup>85</sup>

#### Al Chip Benchmarks

There is no common scheme in the industry for benchmarking CPUs versus AI chips, as comparative chip speed and efficiency depends on the specific benchmark.86 However, for any given node, AI chips typically provide a 10-1,000x improvement in efficiency and speed relative to CPUs, with GPUs and FPGAs on the lower end and ASICs higher.<sup>87</sup> An AI chip 1,000x as efficient as a CPU for a given node provides an improvement equivalent to 26 years of CPU improvements. Table 2 shows our estimates for efficiency and speed gains for GPUs, FPGAs, and ASICs relative to CPUs (normalized at 1x) for DNN training and inference at a given node. No data is available for FPGA training efficiency and speed, as FPGAs are rarely used for training. These estimates are informed by benchmarking studies, which are summarized in Appendix B. Table 2 also lists the generality and inference accuracy of these chips.

Table 2: Comparing state-of-the-art AI chips to state-of-the-art CPUs

|      | Training     |            | Infer       | ence       | Generality <sup>88</sup> | Inference<br>accuracy <sup>89</sup> |

|------|--------------|------------|-------------|------------|--------------------------|-------------------------------------|

|      | Efficiency   | Speed      | Efficiency  | Speed      |                          | ,                                   |

| CPU  | 1 x baseline |            |             |            | Very High                | ~98-99.7%                           |

| GPU  | ~10-100x     | ~10-1,000x | ~1-10x      | ~1-100x    | High                     | ~98-99.7%                           |

| FPGA | -            | -          | ~10-100x    | ~10-100x   | Medium                   | ~95-99%                             |

| ASIC | ~100-1,000x  | ~10-1,000x | ~100-1,000x | ~10-1,000x | Low                      | ~90-98%                             |

# The Value of State-of-the-Art AI Chips

Leading node AI chips are increasingly necessary for cost-effective, fast training and inference of Al algorithms. This is because they exhibit efficiency and speed gains relative to state-of-the-art CPUs (Table 2 and Appendix C) and trailing node AI chips (Figure 7). And, as discussed in subsection A, efficiency translates into overall cost-effectiveness in chip costs—which are the sum of chip production costs (i.e. design, fabrication, assembly, test, and packaging costs). Finally, as discussed in subsection B, cost and speed bottleneck training and inference of many compute-intensive AI algorithms, necessitating the most advanced AI chips for AI developers and users to remain competitive in AI R&D and deployment.

The Efficiency of State-of-the-Art AI Chips Translates into Cost-Effectiveness

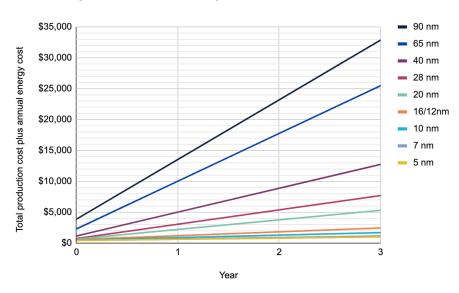

Efficiency translates into overall cost-effectiveness. For trailing nodes, chip operating costs—due to energy consumption costs—dominate chip production costs and quickly balloon to unmanageable levels. Even for leading nodes, operating costs are similar to production costs, implying the need to continue optimizing for efficiency.

Table 3 presents the results of a CSET model of chip production and operating costs for nodes between 90 and 5 nm with the same number of transistors as a generic server-grade 5 nm chip modeled according to the specifications similar to those of the Nvidia P100 GPU. This means that an above-5 nm chip would require a larger surface area. For above-5 nm

nodes, the model could equivalently be interpreted as accounting for production of multiple chips that together have the transistor count of one 5 nm chip. The model takes the perspective of a fabless design firm that, in 2020, designs the chip, buys foundry services from TSMC, then runs the chip in its own server. This mirrors the approach of companies like Google, which designs its TPU in-house, outsources fabrication to TSMC, then runs its TPUs in Google servers for its own Al applications or cloud-computing services to external customers.

The costs break down as follows. The foundry sale price paid by the fabless firm includes capital consumed (i.e. costs of building a fab and purchasing SME), materials, labor, foundry R&D, and profit margin. The fabless firm additionally incurs chip design cost. After fabrication, an outsourced semiconductor and test firm assembles, tests, and packages (ATP) the chip. The sum of foundry sale price, chip design cost, and ATP cost equals the total production cost per chip. The fabless firm also incurs energy cost when operating the chip. We estimate energy cost based on an electricity cost of \$0.07625 per kilowatt-hour. See Appendix D for explanations of how each line-item in Table 3 is calculated. We make two findings.

Table 3: Chip costs at different nodes with 5 nm-equivalent transistor count

|                                                                                  |         |         |                |         |         | 16/   |       |       |       |

|----------------------------------------------------------------------------------|---------|---------|----------------|---------|---------|-------|-------|-------|-------|

| Node (nm)                                                                        | 90      | 65      | 40             | 28      | 20      | 12    | 10    | 7     | 5     |

| Year of mass production                                                          | 2004    | 2006    | 2009           | 2011    | 2014    | 2015  | 2017  | 2018  | 2020  |

| Foundry sale price to fabless firm per chip (i.e. costs + markup)                | \$2,433 | \$1,428 | \$ <i>7</i> 13 | \$453   | \$399   | \$331 | \$274 | \$233 | \$238 |

| Fabless firm's design cost per chip given chip volume of 5 million <sup>90</sup> | \$630   | \$392   | \$200          | \$135   | \$119   | \$136 | \$121 | \$110 | \$108 |

| Assembly, test, and packaging cost per chip                                      | \$815   | \$478   | \$239          | \$152   | \$134   | \$111 | \$92  | \$78  | \$80  |

| Total production cost per chip                                                   | \$3,877 | \$2,298 | \$1,152        | \$740   | \$652   | \$577 | \$487 | \$421 | \$426 |

| Annual energy cost to operate chip                                               | \$9,667 | \$7,733 | \$3,867        | \$2,320 | \$1,554 | \$622 | \$404 | \$242 | \$194 |

First, in less than two years, the cost to operate a leading node Al chip (7 or 5 nm) exceeds the cost of producing said chip, while the cumulative electricity cost of operating a trailing node Al chip (90 or 65 nm) is three to four times the cost of producing that chip.<sup>91</sup> Figure 8 presents total chip costs for

continuous use up to three years: total production cost per chip is added in year zero, with annual energy cost of using the chip added in each subsequent year. These results suggest that leading node AI chips are 33 times more cost-effective than trailing node AI chips when counting production and operating costs. Likewise, because leading node AI chips exhibit one to three orders of magnitude greater efficiency than leading node CPUs (Table 2 and Appendix C), we expect leading node AI chips are also one to three orders of magnitude more cost-effective than leading node CPUs when counting production and operating costs.

Figure 8: Cost of AI chips over time for different nodes

Second, it takes 8.8 years for the cost of producing and operating a 5 nm chip to equal the cost of operating a 7 nm chip. 92 Below 8.8 years, the 7 nm chip is cheaper, and above, the 5 nm chip cheaper. Therefore, users have an incentive to replace existing 7 nm node chips (assuming they do not break down) only when expecting to use 5 nm node chips for 8.8 years. Figure 9 shows node-to-node comparisons between 90 nm and 5 nm. We find that the timeframe where these costs become equal has increased, with a dramatic rise at the 7 versus 5 nm comparison. 93 Firms typically replace server-grade chips after about three years of operation, which is consistent with recent timeframes for introduction of new nodes—that is, firms relying on leading node chips purchase newly introduced node chips as soon as they are available. However, if firms begin purchasing 5 nm node chips, they may expect to use these chips for much longer. 94 This would constitute a market prediction that Moore's Law is slowing, and that the 3 nm node may not be introduced for a long time.95

10.0 Years for old node operating cost = new node total cost 8.8 8.0 6.0 4.3 3.7 4.0 3.0 2.1 1.5 2.0 1.2 0.8 0.0 20 vs. 16/12 16/12 vs. 65 vs. 40 40 vs. 28 10 vs. 7 7 vs. 5

Figure 9: Node transition economics

Comparisons between nodes (nm)

Compute-Intensive AI Algorithms are Bottlenecked by Chip Costs and Speed

Al firms' time and money spent on Al-related computing have become a bottleneck on AI progress. Given leading node AI chips are vastly more costeffective and faster (Table 4 and Figure 7) than trailing node AI chips or leading node CPUs, these AI labs therefore need leading node AI chips to continue Al progress.

First, training costs of Al lab DeepMind's leading Al experiments, such as AlphaGo, AlphaGo Zero, AlphaZero, and AlphaStar, have been estimated at \$5 to \$100 million each. 6 One cost model suggests AlphaGo Zero's training cost was \$35 million. 97,98 AI lab OpenAI reports that of their \$28 million total 2017 costs, \$8 million went to cloud computing. 99 Multiplying these computing costs by thirty for trailing node AI chips, or even more for leading node CPUs, would make such experiments economically prohibitive. And computing costs for some AI companies have increased so quickly that a cost ceiling may soon be reached, necessitating the most efficient Al chips. 100, 101

Second, leading AI experiments can take days or even a month for training, 102 while deployed critical AI systems routinely require fast or realtime inference. Increasing these times by using trailing node AI chips or leading node CPUs would make the required iteration speed for AI R&D and inference speed of deployed critical AI systems unacceptably slow. A

company with slower chips could attempt to pay the enormous energy costs to increase speed by using large numbers of slower chips in parallel. But this gambit would fail for two reasons. For one, as discussed in Section A of Appendix A, leading experiments require AI researchers to tune AI algorithms to support more data and model parallelism. Al researchers can do this to a limited degree, but may face difficulty if attempting to use a dramatically greater number of AI chips in parallel than currently used by leading AI experiments. For another, even if algorithmically possible, such parallelism requires complementary software and networking technology to enable it. 103 Scaling up hundreds or thousands of GPUs in parallel is extremely difficult. 104 Scaling up an even larger number of trailing node GPUs would likely be beyond current capabilities. The new Cerebras Wafer Scale Engine chip presents an intriguing potential workaround to networking technology. It is the first wafer-scale chip, having a much larger surface area than any other Al chip, meaning a large degree of parallelism can be accomplished on a single chip, reducing the need for advanced networking technology between multiple chips. 105

A caveat to this analysis is that some recent AI breakthroughs have not required a significant amount of computing power.<sup>106</sup> Furthermore, there is ongoing research in developing AI algorithms requiring minimal training (e.g. "few shot" learning techniques).<sup>107</sup> For these AI algorithms, multiplying a small cost or speed by a large number may still yield a small cost or speed.

# U.S. and Chinese AI Chips and Implications for National Competitiveness

Cost-effectiveness and speed of leading node AI chips matter from a policy perspective. U.S. companies dominate AI chip design, with Chinese companies far behind in AI chip designs, reliant on U.S. EDA software to design AI chips, and needing U.S. and allied SME and fabs to fabricate AI chips based on these designs. The value of state-of-the-art AI chips, combined with the concentration of their supply chains in the United States and allied countries, presents a point of leverage for the United States and its allies to ensure beneficial development and adoption of AI technologies.<sup>108</sup>

U.S. companies Nvidia and AMD have a duopoly over the world GPU design market, while China's top GPU company, Jingjia Microelectronics, fields dramatically slower GPUs. 109 Likewise, U.S. companies Xilinx and Intel dominate the global FPGA market, while China's leading FPGA companies

Efinix, Gowin Semiconductor, and Shenzhen Pango Microsystem have only developed trailing node FPGAs thus far.<sup>110</sup>

The AI ASIC market, especially for inference, is more distributed with lower barriers to entry, as ASICs and inference chips are easier to design (see Section VI(A)). Unlike GPUs and FPGAs, companies active in AI such as Google, Tesla, and Amazon have begun designing AI ASICs specialized for their own AI applications. Google's TPU is a leading commercial AI ASIC.<sup>111</sup> Intel is also developing powerful commercial AI ASICs,<sup>112</sup> and claims even greater improvements for research ASICs in the range of 10,000x and 1,000x for efficiency and speed respectively.<sup>113</sup> Competitive Chinese companies in the AI ASIC space include Baidu, Alibaba, Tencent, HiSilicon (owned by Huawei), Cambricon Technologies, Intellifusion, and Horizon Robotics. Chinese researchers have also produced high-end research ASICs.<sup>114</sup> However, they are largely limited to inference, although Huawei recently announced the development of an AI training ASIC.<sup>115</sup>

Table 4 lists world-leading server grade U.S. Al chip designs alongside leading Chinese counterparts. 116,117 The data tells two stories.

Table 4: Leading U.S. and Chinese AI chips

| Туре | Firm HQ | Design firm                        | Al chip            | Node (nm)    | Fab     |  |

|------|---------|------------------------------------|--------------------|--------------|---------|--|

| GPU  | United  | AMD <sup>118</sup>                 | Radeon Instinct    | 7            | TSMC    |  |

|      | States  | Nvidia <sup>119</sup>              | Tesla V100         | 12           | TSMC    |  |

|      | China   | Jingjia Micro <sup>120</sup>       | JM7200             | 28           | Unknown |  |

| FPGA | United  | Intel <sup>121</sup> Agilex        |                    | 10           | Intel   |  |

|      | States  | Xilinx <sup>122</sup>              | Virtex             | 16           | TSMC    |  |

|      | China   | Efinix <sup>123</sup>              | Trion              | 40           | SMIC    |  |

|      |         | Gowin Semiconductor <sup>124</sup> | LittleBee          | 55           | TSMC    |  |

|      |         | Shenzhen Pango <sup>125</sup>      | Titan              | 40           | Unknown |  |

| ASIC | United  | Cerebras <sup>126</sup>            | Wafer Scale Engine | 16           | TSMC    |  |

|      | States  | Google <sup>127</sup>              | TPU v3             | 16/12 (est.) | TSMC    |  |

|      |         | Intel <sup>128</sup>               | Habana             | 16           | TSMC    |  |

|       | Tesla <sup>129</sup>            | FSD computer | 10 | Samsung |

|-------|---------------------------------|--------------|----|---------|

| China | Cambricon <sup>130</sup>        | MLU100       | 7  | TSMC    |

|       | Huawei <sup>131</sup>           | Ascend 910   | 7  | TSMC    |

|       | Horizon Robotics <sup>132</sup> | Journey 2    | 28 | TSMC    |

|       | Intellifusion <sup>133</sup>    | NNP200       | 22 | Unknown |

First, Table 4 shows that U.S. Al chip design firms fab exclusively at TSMC, Samsung, or Intel, with chips either at the leading commercial node (7 nm) or close behind. U.S. GPUs use more leading nodes than U.S. FPGAs and ASICs—possibly due to their generality and therefore higher sales volumes that recoup higher leading node design costs.<sup>134</sup>

Experts disagree on the need for leading nodes for AI chips. An executive of the EDA company Cadence Design Systems said, "everybody who wants to do AI needs the performance, power and form factor of 7nm and below." 135 Meanwhile, a semiconductor researcher at Hong Kong Applied Science and Technology Institute was more skeptical: "For AI chips ... manufacturing costs will be much lower if you use 28nm technology and not 10 or 14nm tech ... you need to spend a lot of effort from scratch [to design at leading nodes]—mathematical models, the physical layers, the computational language, all these need investment." 136

The data in Table 4 settles this question: near-leading-edge nodes (i.e.  $\leq 16$  nm) are used for all of the leading U.S. Al chips we investigated. This data is consistent with the CSET chip economics model discussed in Section VI(A). Specifically, the model's results in Figure 8 show an especially high cost-effectiveness for chips at  $\leq 16$  nm, with  $\geq 20$  nm having much higher costs.

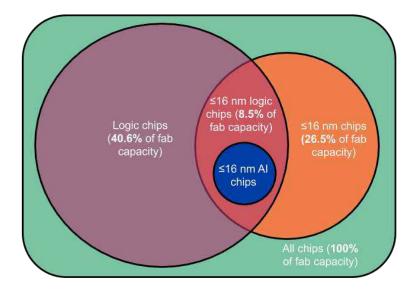

Few fabs are capable of manufacturing near-state-of-the-art Al chips, as shown in Figure 10. Only approximately 8.5% of global fab capacity could be used to fabricate near-state-of-the-art Al chips, and only a subset is currently used for it. The actual percentage used to fabricate near-state-of-the-art Al chips is difficult to calculate and varies year-to-year.

Figure 10: Near-state-of-the-art AI chips comprise a small percentage of all chips 137

Red intersection: chip fab capacity capable of making near-state-of-the-art Al chips

Blue circle: chip fab capacity actually used to make near-state-of-the-art Al chips

Second, Table 4 shows that Chinese AI chip design firms use trailing nodes for GPUs and FPGAs, and a mix of leading nodes and trailing nodes for ASICs. Even though China has some local fabrication capacity at a number of these trailing nodes, China's AI chip design firms still mostly outsource fabrication of trailing node chips to the Taiwanese fab TSMC. This likely reflects TSMC's more reliable fabrication processes than those of Chinese domestic fabs like SMIC. SMIC has capacity as advanced as 14 nm, but only at a low volume. 138 Some of these chip design firms do use SMIC, but SMIC relies on SME imports from the United States, the Netherlands, and Japan. This is because China's SME industry includes only a small number of companies that are not at the state-of-the-art. 139 Chinese AI chip design firms also rely on U.S. EDA software to design their AI chips. Therefore, China remains dependent on the United States and its allies for AI chip production capabilities.

China has achieved the most design success in Al inference ASICs, as its large and well-educated population of engineers is well-suited to the laborintensive work of designing a chip that performs extremely well on a specific task.<sup>140</sup> However, given China's relatively young Al chip design industry, Chinese companies have yet to acquire the implicit know-how needed to navigate the large optimization space and higher complexity of mastering GPUs and FPGAs.

Chinese companies also heavily incorporate Western IP cores into their designs. For example, Huawei licenses British chip design firm ARM's instruction set architecture and IP cores. <sup>141</sup> Chinese FPGA makers also license Intel and Xilinx FPGA IP cores. <sup>142</sup> Licenses for IP cores become exponentially more expensive at leading nodes. <sup>143</sup>

China's lack of development in key sectors of AI chip supply chains—including AI chip designs, EDA software, SME, and fabs—means the United States and its allies maintain a competitive advantage in the production of leading-edge AI chips. As discussed in Section VII, leading-edge AI chips have critical strategic value for the development and deployment of advanced security-relevant AI systems. Therefore, it is vital to U.S., allied, and global security to maintain this advantage.

Future CSET reports will more deeply analyze AI chip industry competitiveness of the United States and China, China's semiconductor industry and its plans for chip independence and supply chain localization, and recommend policies the United States and its allies should pursue to maintain their advantages in the production of AI chips.

# Appendix A: Basics of Semiconductors and Chips

A semiconductor is a material with an electrical conductivity between that of a conductor, which allows the flow of electrical current, and an insulator, which does not. A semiconductor can switch between being conductive and insulative in different circumstances. Silicon is the most commonly used semiconductor. Semiconductors are used in a wide array of devices, such as transistors, resistors, capacitors, and diodes, each of which perform distinct functions. These devices can be manufactured separately as "discrete" devices or multiple devices can be combined into an integrated circuit, also called a "chip."

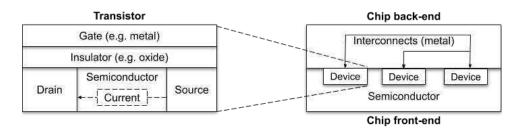

Transistors are especially important devices for computing, as they can be switched between on and off states representing 1 and 0. The metal-oxide-semiconductor field-effect transistor (MOSFET) has been the dominant transistor type since the 1960s. The name is explanatory: a MOSFET includes an insulator (e.g. an oxide) between a gate (e.g. a conductive metal) and a semiconductor channel (e.g. silicon<sup>144</sup>) that connects a source and a drain (see Figure 11). When a voltage (i.e. an electric field) is applied to the gate, the channel is put in an "on" state so that current flows between the source and the drain. When voltage is not applied, the channel is put in an "off" state such that current does not flow between the source and the drain.

The structure of a chip includes a "front-end" and "back-end." The front-end has silicon layers embedded with electrical devices such as transistors. The back-end sits on top of the front-end and consists of layers formed of insulators through which conductive metal wires called interconnects connect the electrical devices of the front-end (see cross-sectional side view in Figure 11). 145 Different combinations of transistors and other electrical devices, wired in particular ways, create various types of "logic gates," which perform basic logical operations. Seven basic logic gates serve as building blocks to create larger "execution units," which implement any desired computation. 146 "Chip design" refers to the layout and structure of these electrical devices and their interconnections.

Figure 11: Transistor and chip structure

Chips today perform virtually all computing and include many types. First, logic chips perform calculations on digital data (Os and 1s) to produce an output. Examples include CPUs, which are general-purpose processors suitable for a wide variety of computing tasks but not specialized for any given tasks, and specialized chips like graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs). GPUs, FPGAs, and ASICs are specialized for improved efficiency and speed for specific applications—such as Al—at the expense of worse-than-CPU efficiency and speed on other applications.

In contrast to logic chips, memory chips store the digital data on which logic devices perform calculations. Examples include "dynamic random-access memory" (DRAM), NAND flash memory, and solid-state hard drives. Analog chips convert between analog (continuous) data and digital (Os and 1s) data. Mixed-signal chips include both digital and analog functions. A system-on-a-chip (SoC) is a single chip that includes all necessary computer functions, including logic functions and memory.<sup>147</sup>

# Appendix B: How AI Chips Work

Al chips implement specific techniques to increase efficiency and speed relative to CPUs. See Figure 12 for a top-down view of a generic Al chip and a pictorial representation of these techniques, which are described in detail in the following subsections.

App Implementing

Domain-Specific

Language

(e.g. TensorFlow)

App Implementing

Domain-Specific

Language

(e.g. TensorFlow)

Instructions

Inst

Figure 12: Generic Al Chip

# Parallel Computing

The most important improvement an AI chip provides over traditional CPUs is parallel computing. AI chips can run a much larger number of simultaneous computations than a CPU can.

Computations for DNNs are especially parallelizable because they are identical and not dependent on the results of other computations. DNN training and inference require a large number of independent, identical matrix multiplication operations, which in turn requires performing many multiplications that are then summed—so called "multiply-and-accumulate" operations. 148,149

Al chip designs typically include large numbers of "multiply-accumulate circuits" (MACs) in a single chip to efficiently perform matrix multiplication operations within a massively parallel architecture. Performing calculations in parallel also enables the AI chip to complete calculations faster than in sequence. Multiple AI chips connected in a parallel architecture can further increase the degree of parallelism. While advanced CPUs have some degree of parallel architectures, AI chips achieve significantly greater parallelism. 152

Parallel processing operations use several techniques. Data parallelism, the most common form of parallelism, splits the input dataset into different "batches," such that computations are performed on each batch in parallel. These batches can be split across different execution units of an AI chip or across different AI chips connected in parallel. Data parallelism works for any type of neural network. Across a wide variety of neural networks, data parallelism using hundreds to thousands of batches during training achieves the same model accuracy without increasing the total number of required computations. However, greater numbers of batches start requiring more compute to achieve the same model accuracy. Beyond a certain number of batches—for some DNNs, over a million—increasing data parallelism requires more compute without any decrease in time spent training the model, thereby imposing a limit on useful data parallelism.<sup>153</sup>

**Model parallelism** splits the model into multiple parts on which computations are performed in parallel on different execution units of an AI chip or across different AI chips connected in parallel.<sup>154</sup> For example, a single DNN layer includes many neurons, and one partition may include a subset of those neurons and another includes a different subset of the same neurons. An alternative technique performs calculations on different neural network layers in parallel.<sup>155</sup>

Given the limits on parallelism, scaling up the amount of compute through more AI chips in parallel is not on its own a viable strategy for further AI progress. <sup>156</sup> Instead, research is necessary to produce AI algorithms allowing greater degrees of data and model parallelism, including research to combine techniques to multiply the degree of parallelism. <sup>157</sup>

### Low-Precision Computing

Low-precision computing—which sacrifices numerical accuracy for speed and efficiency—is especially suitable for Al algorithms. An x-bit processor contains execution units each built to manipulate data that is represented by x bits. A transistor stores a bit, which can take a value of 1 or 0; therefore, x bit values allow  $2^x$  different combinations. Table 5 shows common values of x for processor data types.

Table 5: Data types

| Data types      | 64-bit                    | 32-bit      | 16-bit                   | 8-bit                    |

|-----------------|---------------------------|-------------|--------------------------|--------------------------|

| Possible values | 18 quintillion            | 4.3 billion | 65,536                   | 256                      |

|                 | (1.8 x 10 <sup>19</sup> ) | (4.3 x 10°) | (6.5 x 10 <sup>4</sup> ) | (2.5 x 10 <sup>2</sup> ) |

Higher-bit data types can represent a wider range of numbers (e.g. a larger set of integers) or higher precision numbers within a limited range (e.g. high precision decimal numbers between 0 and 1). Fortunately, with many AI algorithms, training or inference perform as well, or nearly as well, if some calculations are performed with 8-bit or 16-bit data representing a limited or low-precision range of numbers. Even analog computation can suffice for some AI algorithms. These techniques work for the following reasons. First, trained DNNs are often impervious to noise, such that rounding off numbers in inference calculations does not affect results. Second, certain numerical parameters in DNNs are known in advance to have values falling within only a small numerical range—precisely the type of data that can be stored with a low number of bits. 161

Lower-bit data calculations can be performed with execution units containing fewer transistors. This produces two benefits. First, chips can include more parallel execution units if each execution unit requires fewer transistors. Second, lower-bit calculations are more efficient and require fewer operations. An 8-bit execution unit uses 6x less circuit area and 6x less energy than a 16-bit execution unit. 162

#### Memory Optimization

If an Al algorithm's memory access patterns are predictable, Al chips can optimize memory amounts, locations, and types for those predictable uses. 163 For example, some Al chips include sufficient memory to store an entire Al algorithm on-chip. 164 Intra-chip memory access provides major efficiency and speed improvements compared to communication with off-chip memory. Model parallelism becomes an especially useful tool when a model becomes too large to store on a single Al chip; by splitting a model, different portions can be trained on different Al chips connected in parallel. 165

By contrast, most CPUs have a "Von Neumann" design, which includes a single central bus—a communication system that shares data between the CPU and a separate memory chip storing program code and data. Given the bus' limited bandwidth, the CPU must separately access the code and data sequentially and experiences a "Von Neumann bottleneck," whereby memory-access latency prevents CPUs from achieving speeds enabled by high transistor-switching speeds. 166 The Von Neumann design is useful for general-purpose computing. Al chips, on the other hand, do not require a Von Neumann design or exhibit the Von Neumann bottleneck.

#### Domain-Specific Languages

Domain-specific languages (DSLs) provide efficiency gains for specialized applications run on specialized chips.<sup>167</sup>

Programmers use computer languages to write computer code (i.e. instructions to a computer) in a human-understandable way. A computer program called a compiler (or an interpreter) then translates this code into a form directly readable and executable by a processor. Different computer languages operate at various levels of abstraction. For example, a high-level programming language like Python is simplified for human-accessibility, but Python code when executed, is often relatively slow due to complexities of converting high-level instructions for humans into machine code optimized for a specific processor. By contrast, programming languages like C operating at a lower-level of abstraction require more complex code (and effort by programmers), but their code often execute more efficiently because it is easier to convert into machine code optimized for a specific processor. 168 However, both examples are general-purpose programming languages whose code can implement a wide variety of computations, but is not specialized to translate efficiently into machine code for specific computations.

By contrast, DSLs are specialized to efficiently program for and execute on specialized chips. A notable example is Google's TensorFlow, which is DSL whose code runs with higher efficiency on AI chips than any general-purpose language would. Sometimes, the advantages of DSLs can be delivered by specialized code libraries like PyTorch: these code libraries package knowledge of specialized AI-processors in functions that can be called by general-purpose languages (such as Python in this case). 170

## Appendix C: Al Chip Benchmarking Studies

Many researchers have attempted to benchmark DNN efficiency and speed of AI chips against CPUs and each other, with varying results depending on variables including chip type, whether the computation is training or inference, and DNN type (i.e. the benchmark). DNN types include fully connected neural networks (FCNNs), convolutional neural networks (CNNs), recurrent neural networks (RNNs), long short-term memory (LSTM), residual networks (ResNets), and others. Table 6 presents results for a sampling of key recent studies on various comparisons between server grade and PC grade chips. <sup>171</sup> Notably, even some CPUs are being designed with improved AI capabilities (e.g. 200x speed increases), which may reduce the difference between CPU and AI chip results. <sup>172</sup> Finally, all of the chips listed below are U.S. chips, except for the U.K. Graphcore chip and the Chinese Cambricon chip. Little rigorous benchmarking data exists for Chinese AI chips.

Table 6: AI Chip Efficiency and Speed Benchmarking Studies for DNNs

| Author and year                    | Chip comparison                                                        | Computati-<br>on type | DNN types                                              | Efficiency | Speed        |

|------------------------------------|------------------------------------------------------------------------|-----------------------|--------------------------------------------------------|------------|--------------|

| Harvard-1<br>(2019) <sup>173</sup> | Nvidia Tesla<br>V100 <b>GPU</b> vs.<br>Intel Skylake <b>CPU</b>        | Training              | FCNN                                                   | -          | 1-100x       |

|                                    | Google TPU<br>v2/v3 <b>ASIC</b> vs.<br>Nvidia Tesla<br>V100 <b>GPU</b> |                       | CNN, RNN,<br>FCNN                                      | ,          | 0.2-10x      |

| MLPerf<br>(2019) <sup>174</sup>    | Google TPU v3<br>ASIC vs. Nvidia<br>Tesla V100 GPU                     | Training              | ResNet, SSD, R-<br>CNN, NMT,<br>Transformer,<br>MiniGo | -          | 0.8-<br>1.2x |

| Graphcore<br>(2019) <sup>175</sup> | Graphcore IPU<br>ASIC vs. GPU                                          | Training              | Transformer, MLP,<br>Autoencoder,<br>MCMC              | -          | 1-26x        |

|                                    |                                                                        | Inference             | Transformer,<br>ResNext                                | -          | 3-43x        |

| Google<br>(2017) <sup>176</sup>    | Nvidia K80 <b>GPU</b><br>vs. Intel Haswell<br><b>CPU</b>               | Inference             | Weighted average<br>of MLP, CNN,<br>RNN                | 3x         | 2x           |

|                                                    | Improved<br>Google TPU v1<br>ASIC vs. Intel<br>Haswell CPU             |                                         |                                                                                   | 196x   | 50x          |

|----------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|--------|--------------|

| Stanford<br>(2017) <sup>177</sup>                  | Nvidia Tesla K80<br>or P100 <b>GPU</b> vs.                             | Training                                | ResNet                                                                            | -      | 2-12x        |

|                                                    | 16 Intel<br>Broadwell <b>vCPUs</b>                                     | Inference                               |                                                                                   | -      | 5-3x         |